**ESD**

TVS

MOS

LDO

Diode

Sensor

DC-DC

# **Product Specification**

| Domestic Part Number     | BT131 |

|--------------------------|-------|

| Overseas Part Number     | BT131 |

| ▶ Equivalent Part Number | BT131 |

#### **FEATURES**

- Direct interfacing to logic level ICs

- Direct interfacing to low power gate drive circuits and microcontrollers

- High blocking voltage capability

- Planar passivated for voltage ruggedness and reliability

- Triggering in all four quadrants

- Very sensitive gate

### **APPLICATIONS**

- General purpose bi-directional switching and phase control application.

- Air conditioner indoor fan control

- General purpose motor control

- General purpose switching

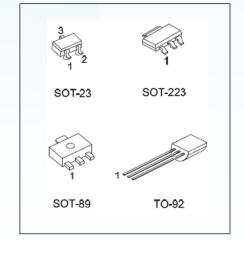

| Package | Pin assignment |    |    |  |

|---------|----------------|----|----|--|

|         | 1              | 2  | 3  |  |

| TO-92   | T1             | G  | T2 |  |

| SOT-223 | T1             | T2 | G  |  |

| SOT-89  | T1             | T2 | G  |  |

| SOT-23  | T1             | G  | T2 |  |

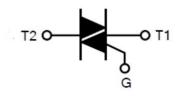

## **SYMBOL:**

#### **ABSOLUTE**

#### **MAXIMUM RATINGS**

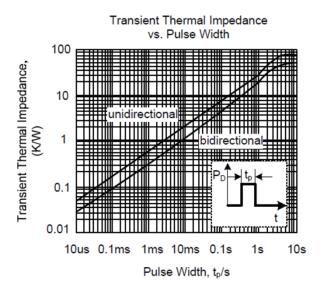

| PARAMETER                                                    | SYMBOL              | VALUE      |     | UNIT             |

|--------------------------------------------------------------|---------------------|------------|-----|------------------|

| Repetitive Peak Off-State Voltages                           | $V_{DRM,} V_{RRM}$  |            | 600 | V                |

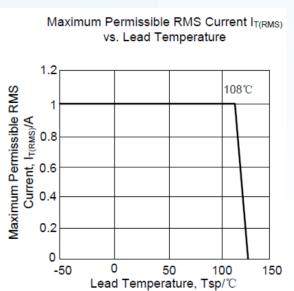

| RMS on-State Current                                         | I <sub>T(RMS)</sub> |            | 1   | А                |

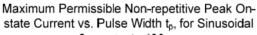

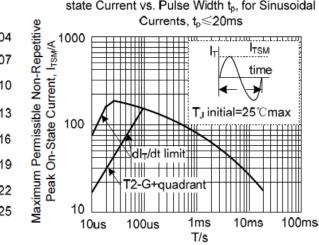

| Non-Repetitive Peak On-State Current                         | I <sub>TSM</sub>    |            | 16  | Α                |

| I <sup>2</sup> t for fusing                                  | l²t                 | 1.28       |     | A <sup>2</sup> s |

| Repetitive rate of rise of on-state current after triggering | dIT/dt              | I          | 50  |                  |

|                                                              |                     | Ш          | 50  | A/uS             |

|                                                              |                     | III        | 50  | A/uS             |

|                                                              |                     | IV         | 10  |                  |

| Peak gate current                                            | I <sub>GM</sub>     | 2          |     | Α                |

| Peak Gate Voltage                                            | $V_{GM}$            | 5          |     | V                |

| Peak Gate Power                                              | $P_GM$              | 5          |     | W                |

| Average Gate Power                                           | $P_{G(AV)}$         | 0.5        |     | W                |

| Operating junction temperature                               | T <sub>J</sub>      | +125       |     | $^{\circ}$       |

| Storage Temperature                                          | T <sub>STG</sub>    | -40 ~ +150 |     | $^{\circ}$       |

# **ELECTRICAL CHARACTERISTICS** (TJ=25°C)

| PARAMETER                                           | SYMBOL                               | TEST CONDITIO                                | MIN | MAX | UNITS |      |

|-----------------------------------------------------|--------------------------------------|----------------------------------------------|-----|-----|-------|------|

| Peak Repetitive Forward or Reverse Blocking Current | I <sub>DRM</sub><br>I <sub>RRM</sub> | V <sub>AK</sub> = Rated V <sub>DRN</sub>     |     | 0.5 | mA    |      |

| Gate Trigger Current                                | I <sub>GT</sub>                      | $V_D=12V$ , $R_L=100\Omega$                  | I   |     | 5.0   | mA   |

|                                                     |                                      |                                              | II  |     | 5.0   |      |

|                                                     |                                      |                                              | III |     | 5.0   |      |

|                                                     |                                      |                                              | IV  |     | 10    |      |

| Gate Trigger Voltage                                | V <sub>GT</sub>                      | V <sub>D</sub> =12V, I <sub>T</sub> =100mA   |     |     | 1.5   | V    |

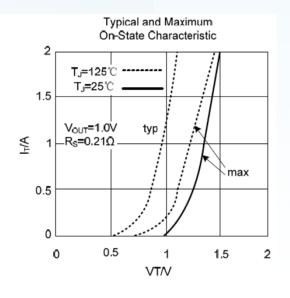

| Peak Forward On-State<br>Voltage                    | $V_{TM}$                             | IT=2.0A                                      |     | 1.5 | V     |      |

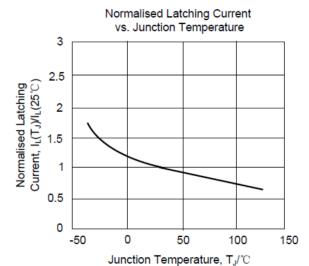

| Latch Current                                       | IL                                   | V <sub>D</sub> =12V<br>I <sub>G</sub> =0.1A, | I   |     | 5.0   |      |

|                                                     |                                      |                                              | II  |     | 8.0   | mA   |

|                                                     |                                      |                                              | III |     | 5.0   |      |

|                                                     |                                      |                                              | IV  |     | 5.0   |      |

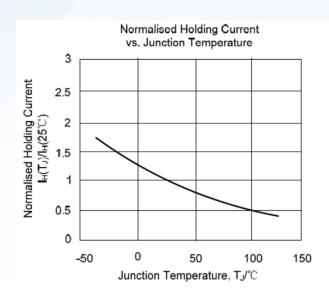

| Holding Current                                     | I <sub>H</sub>                       | V <sub>D</sub> =12V ,I <sub>G</sub> =0.1A    |     |     | 5     | mA   |

| Gate Non-Trigger Voltage                            | $V_{\sf GD}$                         | $V_D = V_{DRM}$                              |     | 0.2 |       | V    |

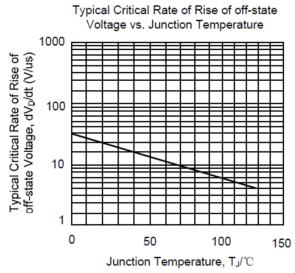

| Critical Rate of Rise of Off-State Voltage          | dV/dt                                | $V_D$ =67% $V_{DRM}$ , $R_{GK}$ =1k $\Omega$ |     | 5   |       | V/µs |

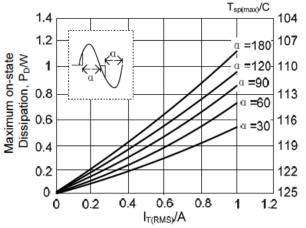

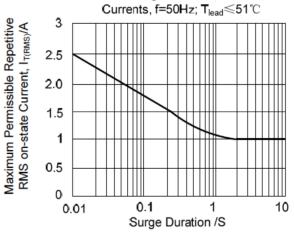

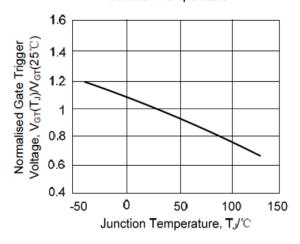

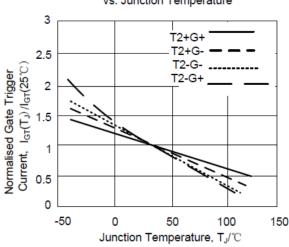

#### **ELECTRICAL CHARACTERISTIC CURVE**

Maximum Permissible Repetitive RMS on-state Current vs. Surge Duration, for Sinusoidal

Normalised Gate Trigger Voltage vs. Junction Temperature

Normalised Gate Trigger Current vs. Junction Temperature

# Disclaimer

EVVOSEMI ("EVVO") reserves the right to make corrections, enhancements, improvements, and other changes to its products and services at any time, and to discontinue any product or service without notice.

EVVO warrants the performance of its hardware products to the specifications applicable at the time of sale in accordance with its standard warranty. Testing and other quality control techniques are used as deemed necessary by EVVO to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

Customers should obtain and confirm the latest product information and specifications before final design, purchase, or use. EVVO makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does EVVO assume any liability for application assistance or customer product design. EVVO does not warrant or accept any liability for products that are purchased or used for any unintended or unauthorized application.

EVVO products are not authorized for use as critical components in life support devices or systems without the express written approval of EVVOSEMI.

The EVVO logo and EVVOSEMI are trademarks of EVVOSEMI or its subsidiaries in relevant jurisdictions. EVVO reserves the right to make changes without further notice to any products herein.