**ESD**

TVS

MOS

LDO

Diode

Sensor

DC-DC

# **Product Specification**

| Domestic Part Number     | 74HC595D |

|--------------------------|----------|

| Overseas Part Number     | 74HC595D |

| ▶ Equivalent Part Number | 74HC595D |

# 8-bit serial-in/serial or parallel-out shift register with output latches; 3-state

#### Description:

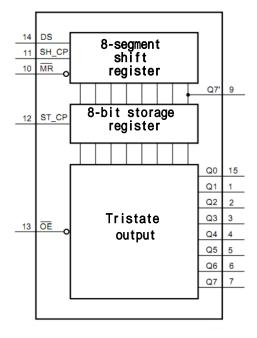

74HC595 is a high-speed silicon gate CMOS device with pins compatible with low-power Schottky TTL circuits (LSTTL). It complies with JEDEC standard No.7A. It consists of eight serial shift registers with storage registers and three state outputs. The shift register and storage register have separate clocks. Data in shift clock SH\_ When the rising edge of CP arrives, shift transmission is performed, while the storage clock ST\_

When the rising edge of CP arrives, it is transferred from the shift register to the storage register. If two clocks are connected together, the data on the shift register is always one clock pulse ahead of the storage register. The shift register has a serial input (DS) and a cascaded serial output (Q7 '), as well as an asynchronous reset (effective at low levels).

The storage register has an eight bit parallel bus driver output with a three state output. When the output enable end (OE) is at low level, the output end is normal output. Conversely, when OE is at high level, the output is in high resistance off state.

#### Features:

- -Eight bit serial input

- -Eight bit serial or parallel output

- -Shift output frequency ESD protection

function at 100MHz (typical value)

-A storage register with a three state output and a shift register with direct zeroing

#### Application:

- -serial parallel conversion

- -Remote control memory retention

device

#### Absolute Maximum Ratings

| parameter               | symbol    | Test conditions                                                       | min   | max | unit       |

|-------------------------|-----------|-----------------------------------------------------------------------|-------|-----|------------|

| supply voltage          | Vcc       |                                                                       | -0. 5 | 7   | V          |

| Input diode current     | IIK       | VI<-0.5V or VI>Vcc+0.5V                                               | -     | ±20 | mA         |

| Output diode<br>current | 1оК       | Vo<-0.5V or Vo>Vcc+0.5V                                               | -     | ±20 | mA         |

| Output pouring          |           | -0.5V <vo<vcc+0.5v< td=""><td>-</td><td></td><td></td></vo<vcc+0.5v<> | -     |     |            |

| current or pulling      | 10        | Q' standard output                                                    | -     | ±25 | mA         |

| current                 |           | Q0~Q7 bus drive output                                                | _     | ±35 | mA         |

| Vcc, GND current        | Icc, IGND |                                                                       | _     | ±70 | mA         |

| storage temperature     | Tstg      |                                                                       | -65   | 150 | $^{\circ}$ |

| consumption             | Ptot      | Tamb=-40 to 125℃                                                      | _     | 500 | mW         |

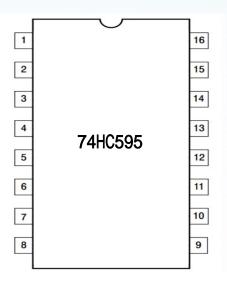

# Pin Assignment:

## DIP/SOP16

| pin no. | symbol | function description                             |

|---------|--------|--------------------------------------------------|

| 1       | Q1     | Parallel output terminal                         |

| 2       | Q2     | Parallel output terminal                         |

| 3       | Q3     | Parallel output terminal                         |

| 4       | Q4     | Parallel output terminal                         |

| 5       | Q5     | Parallel output terminal                         |

| 6       | Q6     | Parallel output terminal                         |

| 7       | Q7     | Parallel output terminal                         |

| 8       | GND    | grounding(OV)                                    |

| 9       | Q7'    | Serial output terminal                           |

| 10      | MR     | Main reset (effective at low level)              |

| 11      | SH_CP  | Shift register clock input                       |

| 12      | ST_CP  | Memory register clock input terminal             |

| 13      | ŌĒ     | Output enabling terminal(effective at low level) |

| 14      | DS     | Serial input terminal                            |

| 15      | Q0     | Parallel output terminal                         |

| 16      | Vcc    | power supply                                     |

#### menubar

|          | input    |    |    |    |       | tput |                                                                                                                                                                                        |  |

|----------|----------|----|----|----|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SH_CP    | ST_CP    | ŌĒ | MR | DS | Q7'   | Qn   | function                                                                                                                                                                               |  |

| ×        | ×        | L  | L  | ×  | L     | n. c | MR only resets the shift register when the power level is low                                                                                                                          |  |

| ×        | <b>†</b> | L  | L  | ×  | L     | L    | Shift register transfers null values to storage registers                                                                                                                              |  |

| ×        | ×        | Н  | L  | ×  | L     | Z    | Clear the shift register to zero; Parallel output in                                                                                                                                   |  |

| <b>†</b> | ×        | L  | Н  | Н  | Q6'   | n. c | The logic high level is transmitted from the input to the shift register of segment 0; The data of all shift registers is sequentially transmitted under the action of the shift clock |  |

| ×        | 1        | L  | Н  | ×  | n. C, | Qn'  | All shift register data is transmitted to the corresponding storage registers under the action of the storage clock                                                                    |  |

| <b>†</b> | t        | L  | Н  | ×  | Q6'   | Qn'  | The shift register is sequentially passed back;<br>Simultaneously shifting the register to transfer<br>the previous state to the corresponding storage<br>register and output          |  |

Note: H=high level L=low level Z=high resistance closed state X=irrelevant quantity

falling edge n.c.=no change

rising edge

### function diagram

Figure 3 Functional Diagram

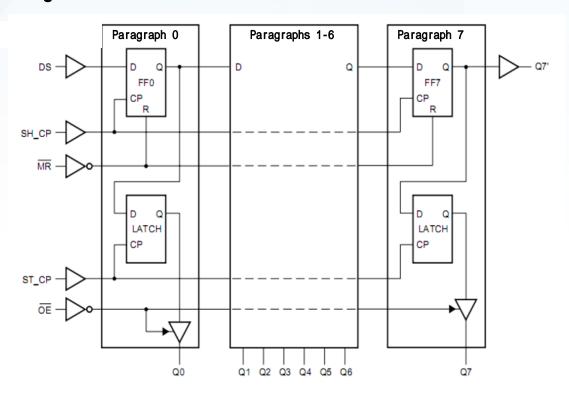

## logic diagram

Figure 4 Logic Diagram

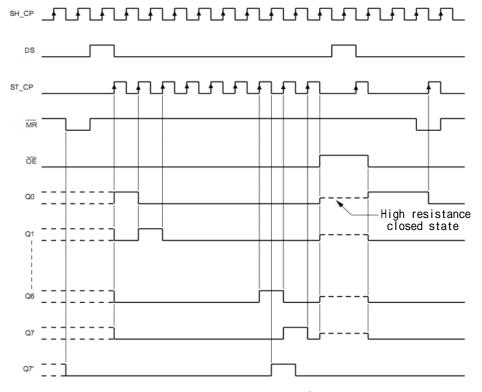

## Timing Diagram

Figure 5 Timing Chart

# **DC parameters** (ambient temperature: -40~+125 ; all typical values are tested at 25 )

| parameter                                  | symbol | Test condit                                     | ions           | min            | typ            | max                  | unit   |

|--------------------------------------------|--------|-------------------------------------------------|----------------|----------------|----------------|----------------------|--------|

| parameter                                  | Symbol | condition                                       | Vcc(V)         |                |                | IIIdX                |        |

|                                            |        |                                                 | 2              | 1.5            | 1.2            | _                    | V      |

| High Level Input Voltage                   | VIH    |                                                 | 4. 5           | 3. 15          | 2. 4           | _                    | V      |

|                                            |        |                                                 | 6              | 4. 2           | 3. 2           | -                    | V      |

| low level input                            | WII    |                                                 | 2              | _              | 0.8            | 0.5                  | V      |

| voltage                                    | VIL    |                                                 | 4. 5<br>6      | _              | 2. 1           | 1. 35                | V      |

|                                            |        | VI=VIH or VIL                                   | O              |                | 2.8            | 1.8                  | V      |

|                                            |        |                                                 | 2              | 1. 9           | 2              | _                    | V      |

|                                            |        | All outputs                                     | 4. 5           | 4. 4           | 4. 5           | _                    | V      |

|                                            |        | 1o=-20uA                                        | 6              | 5. 9           | 6              | _                    | V      |

| high level output voltage                  | VOH    | Q7'Standard output terminal lo=-4.0mA lo=-5.2mA | 4. 5<br>6      | 3. 84<br>5. 34 | 4. 32<br>5. 81 | -                    | V<br>V |

|                                            |        | Qn bus drive                                    |                |                |                |                      |        |

|                                            |        | output<br>10=-6.0mA<br>10=-7.8mA                | 4. 5<br>6      | 3. 84<br>5. 34 | 4. 32<br>5. 81 | _<br>_               | V<br>V |

|                                            |        | VI=VIH or VIL                                   |                |                |                |                      |        |

|                                            |        | All outputs<br>lo=-20uA                         | 2<br>4. 5<br>6 | _<br>_<br>_    | 0 0 0          | 0. 1<br>0. 1<br>0. 1 | V      |

| Low Level Output Voltage                   | VOL    | output terminal                                 |                |                |                | 0.1                  | •      |

| Low Level output vortage                   | VOL    | 1o=-4. OmA                                      | 4.5            | _              | 0.15           | 0.33                 |        |

|                                            |        | 1o=-5. 2mA                                      | 6              | _              | 0.16           | 0.33                 | V      |

|                                            |        | output                                          |                |                |                |                      |        |

|                                            |        | 1o=-6.0mA                                       | 4. 5           | _              | 0. 16          | 0.33                 |        |

|                                            |        | 1o=-7.8mA                                       | 6              | _              | 0. 16          | 0.33                 | V      |

| Input peak current                         | IL     | VI=Vcc or GND                                   | 6              | _              | _              | ±1                   | uA     |

| Three state output high resistance current | loz    | VI=VIH or VIL<br>Vo=Vcc or GND                  | 6              | _              | _              | ±5                   | uA     |

| Static power supply current                | Icc    | VI=Vcc or GND<br>1o=0                           | 6              | _              | -              | 80                   | uA     |

# ambient temperature: -40 ~+125

| parameter                                  | symbol | Test conditions                             |        | min typ      |     | yp max | unit |

|--------------------------------------------|--------|---------------------------------------------|--------|--------------|-----|--------|------|

| per ane cer                                | Symbol | condition                                   | Vcc(V) | IIIIII       | сур | max    | unit |

|                                            |        |                                             | 2      | 1.5          | -   | -      | V    |

| High Level Input Voltage                   | VIH    |                                             | 4. 5   | 3. 15        | -   | -      | V    |

|                                            |        |                                             | 6      | 4.2          | -   | -      | V    |

|                                            |        |                                             | 2      | -            | -   | 0. 5   | V    |

| low level input voltage                    | VIL    |                                             | 4. 5   | -            | -   | 1.35   | V    |

|                                            |        |                                             | 6      | -            | -   | 1.8    | V    |

|                                            |        | VI=VIH or VIL                               |        |              |     |        |      |

|                                            |        | ALL outputs                                 | 2      | 1.9          | -   | -      | V    |

|                                            |        | 1o=-20uA                                    | 4. 5   | 4.4          | -   | -      | V    |

|                                            |        | 1020uA                                      | 6      | 5. 9         | -   | -      | V    |

| high level output voltage                  | VOH    | Q7'Standard output terminal 10=-4.0mA       | 4. 5   | 3. 7         | _   | _      | V    |

| night level output voltage                 | VOII   | 10= 4. OllA<br>10=-5. 2mA                   | 6      | 5. 2         | _   | _      | V    |

|                                            |        | Qn bus drive output lo=-6.0mA lo=-7.8mA     | 4.5    | 3. 7<br>5. 2 | -   | -      | V    |

|                                            |        | VI=VIH or VIL                               |        |              |     |        |      |

|                                            |        | ALL outputs<br>1o=-20uA                     | 4. 5   | -            | -   | 0. 1   | V    |

| Low Level Output Voltage                   | VOL    | Q7'Standard<br>output terminal<br>lo=-4.0mA | 4. 5   | -            | -   | 0.4    | V    |

|                                            |        | Qn bus drive<br>output<br>lo=-6.0mA         | 4. 5   | -            | -   | 0.4    | V    |

| Input peak current                         | ILI    | VI=Vcc or GND                               | 5. 5   | -            | -   | ±1     | uA   |

| Three state output high resistance current | Ioz    | VI=VIH or VIL<br>Vo=Vcc or GND              | 5. 5   | -            | -   | ±10    | uA   |

| Static power supply current                | Icc    | VI=Vcc or GND<br>lo=0                       | 5. 5   | -            | -   | 160    | uA   |

AC parameters (GND=0V; tr-tf-6ns; CL=50Pf)

ambient temperature: 25

|                                              | 1 1             | Test condit    | ions   |     |     |     | • .  |

|----------------------------------------------|-----------------|----------------|--------|-----|-----|-----|------|

| parameter                                    | symbol          | wave form      | Vcc(V) | min | typ | max | unit |

|                                              |                 |                | 2      | _   | 52  | 160 | ns   |

| Transmission delay time                      |                 | See Figure 6   | 4. 5   | _   | 19  | 32  | ns   |

| from SH_CP to Q7'                            | - DIII /- DI II |                | 6      | _   | 15  | 27  | ns   |

|                                              | tPHL/tPLH       |                | 2      | -   | 55  | 175 | ns   |

| ST_CP to Qn transmission                     |                 | See Figure 7   | 4. 5   | _   | 20  | 35  | ns   |

| delay time                                   |                 |                | 6      | _   | 16  | 30  | ns   |

|                                              |                 |                | 2      | _   | 47  | 175 | ns   |

| Transmission delay time                      | tPHL            | See Figure 9   | 4. 5   | _   | 17  | 35  | ns   |

| from MR to Q7'                               |                 |                | 6      | -   | 14  | 30  | ns   |

| OE causes Qn terminal to                     |                 |                | 2      | _   | 47  | 30  | ns   |

| transition from high                         | . D             |                | 4. 5   | _   | 17  | 150 | ns   |

| resistance state to enable output time       | tPZH/tPZL       | See Figure 10  | 6      | -   | 14  | 30  | ns   |

| OF 11 11 0                                   |                 |                | 2      | _   | 41  | 26  | ns   |

| OE enables the Qn<br>terminal to output from |                 |                | 4.5    | _   | 15  | 150 | ns   |

| enable to high resistance<br>state time      | tPHZ/tPLZ       | See Figure 10  | 6      | -   | 12  | 30  | ns   |

|                                              |                 | See Figure 6   | 2      | 75  | 17  | 26  | ns   |

| Shift clock pulse width (high or low level)  |                 |                | 4. 5   | 15  | 6   | _   | ns   |

| (High of low level)                          |                 |                | 6      | 13  | 5   | _   | ns   |

| Store clock pulse width                      |                 |                | 2      | 75  | 11  |     | ns   |

|                                              | tW              | See Figure 7   | 4. 5   | 15  | 4   | _   | ns   |

| (high or low level)                          |                 |                | 6      | 13  | 3   | _   | ns   |

| Wain mand and a middle                       |                 | See Figure 9   | 2      | 75  | 17  |     | ns   |

| Main reset pulse width (low level)           |                 |                | 4. 5   | 15  | 6   | -   | ns   |

| (10w level)                                  |                 |                | 6      | 13  | 5   |     | ns   |

|                                              |                 |                | 2      | 50  | 11  | -   | ns   |

| Establishment time from DS to SH_CP          |                 | See Figure 8   | 4.5    | 10  | 4   |     | ns   |

| D5 t0 5H_Cl                                  | tau             |                | 6      | 9   | 3   | _   | ns   |

|                                              | tsu             |                | 2      | 75  | 22  | -   | ns   |

| Establishment time from SH_CP to ST_CP       |                 | See Figure 7   | 4.5    | 15  | 8   | _   | ns   |

| SII_CI to SI_CI                              |                 |                | 6      | 13  | 7   | _   | ns   |

| DO 1 GH OD - 1 - 1                           |                 |                | 2      | 3   | -6  | _   | ns   |

| DS to SH_CP retention                        | th              | See Figure 8   | 4. 5   | 3   | -2  |     | ns   |

| time                                         |                 |                | 6      | 3   | -2  |     | ns   |

| MD 11 CW CD                                  |                 |                | 2      | 50  | -19 | -   | ns   |

| MR enables SH CP reset                       | trem            | See Figure 9   | 4. 5   | 10  | -7  | _   | ns   |

| time                                         |                 |                | 6      | 9   | -6  | -   | ns   |

| Windows I and I                              |                 |                | 2      | 9   | 30  | _   | MHZ  |

| Minimum clock pulse                          | fmax            | See Figure 6,7 | 4. 5   | 30  | 91  | -   | MHZ  |

| width of SH_CP or ST_CP                      |                 |                | 6      | 35  | 108 | _   | MHZ  |

#### ambient temperature: -40 ~85

|                                           | Test conditions |                           |        |     |     |     |        |

|-------------------------------------------|-----------------|---------------------------|--------|-----|-----|-----|--------|

| parameter                                 | symbol          | wave form                 | Vcc(V) | min | typ | max | unit   |

| m                                         |                 |                           | 2      | _   | -   | 200 | ns     |

| Transmission delay time from SH_CP to Q7' |                 | See Figure 6              | 4.5    | _   | _   | 40  | ns     |

| 110m Sn_cr to Q1                          | +DIII /+DI II   |                           | 6      | _   | _   | 34  | ns     |

|                                           | tPHL/tPLH       |                           | 2      | _   | _   | 220 | ns     |

| ST_ CP to Qn transmission delay time      |                 | See Figure 7              | 4.5    | _   | _   | 44  | ns     |

| delay time                                |                 |                           | 6      | _   | _   | 37  | ns     |

|                                           |                 |                           | 2      | _   | _   | 220 | ns     |

| Transmission delay time<br>from MR to Q7' | tPHL            | See Figure 9              | 4.5    | _   | _   | 44  | ns     |

| Troil Mr. to Q1                           |                 |                           | 6      | _   | -   | 37  | ns     |

| OE causes Qn terminal to                  |                 |                           | 2      | -   | -   | 190 | ns     |

| transition from high                      | tPZH/tPZL       | See Figure 10             | 4. 5   | _   | -   | 38  | ns     |

| resistance state to enable                |                 |                           | 6      | _   | -   | 33  | ns     |

| OE enables the Qn                         |                 |                           | 2      | _   | -   | 190 | ns     |

| terminal to output from                   | tPHZ/tPLZ       | See Figure 10             | 4. 5   | _   | -   | 38  | ns     |

| enable to high resistance                 |                 |                           | 6      | _   | _   | 33  | ns     |

|                                           | tW              | See Figure 6 See Figure 7 | 2      | 95  | _   | _   | ns     |

| Shift clock pulse width                   |                 |                           | 4. 5   | 19  | -   | -   | ns     |

| (high or low level)                       |                 |                           | 6      | 16  | _   | _   | ns     |

|                                           |                 |                           | 2      | 95  | _   | _   | ns     |

| Store clock pulse width                   |                 |                           | 4. 5   | 19  | -   | -   | ns     |

| (high or low level)                       |                 |                           | 6      | 16  | _   | _   | ns     |

|                                           |                 |                           | 2      | 95  | _   | _   | ns     |

| Main reset pulse width                    |                 | See Figure 9              | 4. 5   | 19  | -   | -   | ns     |

| (low level)                               |                 |                           | 6      | 16  | _   | _   | ns     |

|                                           |                 |                           | 2      | 65  | -   | _   | ns     |

| Establishment time from                   |                 | See Figure 8              | 4. 5   | 13  | -   | -   | ns     |

| DS to SH_ CP                              |                 |                           | 6      | 11  | -   | _   | ns     |

|                                           | tsu             |                           | 2      | 95  | _   | _   | ns     |

| Establishment time from                   |                 | See Figure 7              | 4. 5   | 19  | -   | -   | ns     |

| SH_ CP to ST_ CP                          |                 |                           | 6      | 16  | _   | _   | ns     |

|                                           |                 |                           | 2      | 3   | -   | -   | ns     |

| DS to SH_ CP retention                    | th              | See Figure 8              | 4. 5   | 3   | -   | _   | ns     |

| time                                      |                 |                           | 6      | 3   | _   | _   | ns     |

|                                           |                 |                           | 2      | 65  | -   | _   | ns     |

| MR enables SH_ CP reset                   | trem            | See Figure 9              | 4. 5   | 13  | -   | _   | ns     |

| time                                      | CT GIII         |                           | 6      | 11  |     | _   | ns     |

|                                           |                 |                           | 2      | 4.8 | _   | _   | MHZ    |

| Minimum clock pulse                       | fmax            | See Figure 6,7            | 4.5    | 24  | _   | _   | MHZ    |

| width of SH_ CP or ST_ CP                 | LIIGA           | 500 118410 0,1            | 6      | 28  | _   | _   | MHZ    |

|                                           |                 |                           |        | 20  |     |     | 111112 |

#### ambient temperature: -40 ~125

|                                            | 1 1          | Test conditi                  | ions   |     |     |     |      |

|--------------------------------------------|--------------|-------------------------------|--------|-----|-----|-----|------|

| parameter                                  | symbol       | wave form                     | Vcc(V) | min | typ | max | unit |

| Thomasian dalay time                       |              |                               | 2      | -   | -   | 240 | ns   |

| Transmission delay time from SH_ CP to Q7' |              | See Figure 6                  | 4. 5   | -   | -   | 48  | ns   |

|                                            | +DIII /+DIII |                               | 6      | -   | -   | 41  | ns   |

| CT CD to On town in its                    | tPHL/tPLH    |                               | 2      | -   | -   | 265 | ns   |

| ST_ CP to Qn transmission delay time       |              | See Figure 7                  | 45     | -   | -   | 53  | ns   |

| deray time                                 |              |                               | 6      | -   | -   | 45  | ns   |

| T                                          |              |                               | 2      | -   | -   | 265 | ns   |

| Transmission delay time from MR to Q7'     | tPHL         | See Figure 9                  | 4. 5   | -   | -   | 53  | ns   |

| 110m will to Q1                            |              |                               | 6      | -   | -   | 45  | ns   |

| OE causes Qn terminal to                   |              |                               | 2      | -   | -   | 225 | ns   |

| transition from high                       | tPZH/tPZL    | See Figure 10                 | 4. 5   | -   | -   | 45  | ns   |

| resistance state to enable                 |              |                               | 6      | -   | -   | 35  | ns   |

| OE enables the Qn                          |              |                               | 2      | _   | -   | 225 | ns   |

| terminal to output from                    | tPHZ/tPLZ    | See Figure 10                 | 4. 5   | -   | -   | 45  | ns   |

| enable to high resistance                  |              |                               | 6      | -   | -   | 35  | ns   |

| Shift clock pulse width                    |              |                               | 2      | 110 | -   | -   | ns   |

| -                                          |              | See Figure 6  tW See Figure 7 | 4. 5   | 22  | -   | -   | ns   |

| (high or low level)                        |              |                               | 6      | 19  | -   | -   | ns   |

| Store clock pulse width                    |              |                               | 2      | 110 | -   | -   | ns   |

|                                            | tW           |                               | 4. 5   | 22  | -   | -   | ns   |

| (high or low level)                        |              |                               | 6      | 19  | -   | -   | ns   |

| Main reset pulse width                     |              |                               | 2      | 110 | -   | -   | ns   |

| •                                          |              | See Figure 9                  | 4. 5   | 22  | -   | ı   | ns   |

| (low level)                                |              |                               | 6      | 19  | -   | -   | ns   |

| B                                          |              |                               | 2      | 75  |     | -   | ns   |

| Establishment time from                    |              | See Figure 8                  | 4.5    | 15  | -   | -   | ns   |

| DS to SH_ CP                               | 4            |                               | 6      | 13  | -   | -   | ns   |

| F-4-1-1:-1                                 | tsu          |                               | 2      | 110 | -   | -   | ns   |

| Establishment time from SH_ CP to ST_ CP   |              | See Figure 7                  | 4. 5   | 22  | -   | -   | ns   |

| 311_ C1 t0 31_ C1                          |              |                               | 6      | 19  | -   | -   | ns   |

| DG 1 GH GD - 1                             |              |                               | 2      | 3   | -   | -   | ns   |

| DS to SH_ CP retention time                | th           | See Figure 8                  | 4. 5   | 3   | -   | -   | ns   |

| time                                       |              |                               | 6      | 3   | -   | -   | ns   |

| WD 1.1 - 2W - 2D                           |              |                               | 2      | 75  | -   | -   | ns   |

| MR enables SH_ CP reset                    | trem         | See Figure 9                  | 4. 5   | 15  | -   | -   | ns   |

| time                                       |              |                               | 6      | 13  | -   | -   | ns   |

|                                            |              |                               | 2      | 4   | -   | -   | MHZ  |

| Minimum clock pulse                        | fmax         | See Figure 6,7                | 4. 5   | 20  | -   | -   | MHZ  |

| width of SH_ CP or ST _ CP                 |              |                               | 6      | 24  | -   | -   | MHZ  |

#### AC waveform

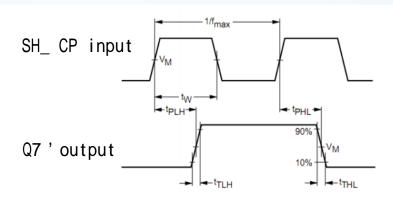

Figure 6: The above figure shows the transmission delay time, shift clock pulse width, and maximum shift clock frequency

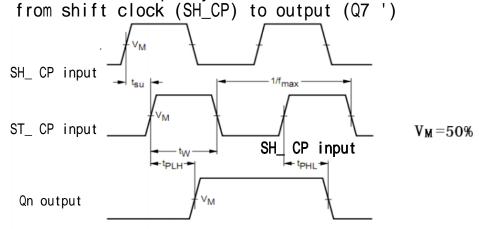

Figure 7: The above figure shows the transmission delay time from storage clock (ST\_CP) to output (Qn), storage clock pulse width, and establishment time from shift clock to storage clock

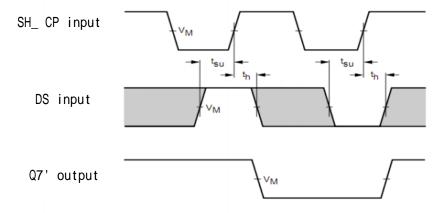

Figure 8: The above figure shows the establishment and retention time of DS input

Note: The shaded portion indicates that the input signal has no effect on the output at this time

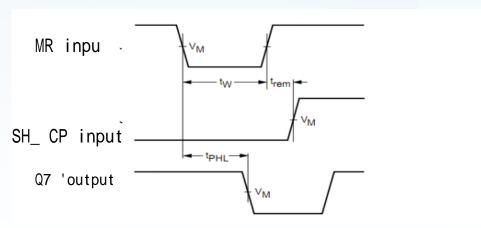

Figure 9: The above figure shows the pulse width of the main reset (MR), the transmission delay time from the main reset to the output (Q7 '), and the reset time from the main reset to the shift clock (SH CP)

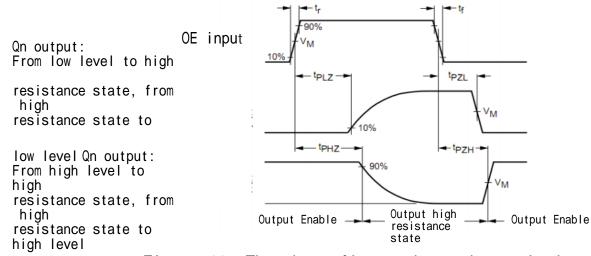

Figure 10: The above figure shows the variation time of the three state output with the output enable end

## Pin Assignment:

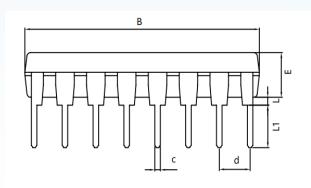

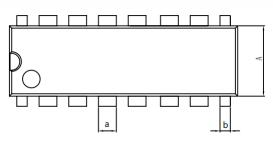

### DIP16

| Dimensions In Millimeters |         |         |         |           |       |  |  |  |  |  |

|---------------------------|---------|---------|---------|-----------|-------|--|--|--|--|--|

| Symbol:                   | Min:    | Max:    | Symbol: | Min:      | Max:  |  |  |  |  |  |

| A                         | 6. 100  | 6. 680  | L       | 0. 500    | 0.800 |  |  |  |  |  |

| В                         | 18. 940 | 19. 560 | a       | 1.524 TYP |       |  |  |  |  |  |

| D                         | 8. 200  | 9. 200  | b       | 0.889 TYP |       |  |  |  |  |  |

| D1                        | 7. 42   | 7. 820  | С       | 0. 457    | 7 TYP |  |  |  |  |  |

| Е                         | 3. 100  | 3. 550  | d       | 2. 540    | ) TYP |  |  |  |  |  |

| L                         | 0. 500  | 0.800   |         |           |       |  |  |  |  |  |

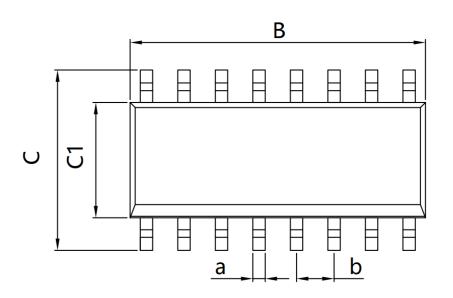

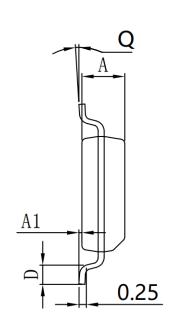

## S0P16

| Dimensions In Millimeters |        |        |         |           |       |  |  |  |  |

|---------------------------|--------|--------|---------|-----------|-------|--|--|--|--|

| Symbol:                   | Min:   | Max:   | Symbol: | Min:      | Max:  |  |  |  |  |

| A                         | 1. 225 | 1. 570 | D       | 0.400     | 0.950 |  |  |  |  |

| A1                        | 0. 100 | 0. 250 | Q       | 0°        | 8°    |  |  |  |  |

| В                         | 9.800  | 10.00  | a       | 0.420 TYP |       |  |  |  |  |

| С                         | 5. 800 | 6. 250 | b       | 1.270 TYP |       |  |  |  |  |

| C1                        | 3.800  | 4. 000 |         |           |       |  |  |  |  |

### Disclaimer

EVVOSEMI ("EVVO") reserves the right to make corrections, enhancements, improvements, and other changes to its products and services at any time, and to discontinue any product or service without notice.

EVVO warrants the performance of its hardware products to the specifications applicable at the time of sale in accordance with its standard warranty. Testing and other quality control techniques are used as deemed necessary by EVVO to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

Customers should obtain and confirm the latest product information and specifications before final design, purchase, or use. EVVO makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does EVVO assume any liability for application assistance or customer product design. EVVO does not warrant or accept any liability for products that are purchased or used for any unintended or unauthorized application.

EVVO products are not authorized for use as critical components in life support devices or systems without the express written approval of EVVOSEMI.

The EVVO logo and EVVOSEMI are trademarks of EVVOSEMI or its subsidiaries in relevant jurisdictions. EVVO reserves the right to make changes without further notice to any products herein.